# ヘテロジニアスマルチコアプロセッサの RISC-V 移植に関する研究

柏森 風介 指導教員:佐々木 敬泰

### 1 はじめに

コンピュータの省電力化、高速化のために複数の異なるプロセッサコアを組み合わせるヘテロジニアスマルチコアプロセッサ (Heterogeneous Multicore Processor: HMP) が提案されているが、HMP はその設計に非常に大きな労力が必要となる。その問題を解決するために HMP の自動設計ツールとしてFabHetero が提案されている。しかし、この自動設計ツールは現在は商用ではほとんど利用されていない古い命令セットにしか対応していない。そこで本研究ではこの自動設計ツールを最新の命令セットである RISC-V に対応させることを目標に、命令セットの変更に伴い新たに実装する必要のある命令の実装方法を提案し、その命令を実行する LSU を作成・評価を行った。

### 2 関連研究

#### 2.1 FabHetero

前述の通り、FabHetero はヘテロジニアスマルチコアプロセッサの自動設計ツールである。現在、FabHetero はプロセッサコア生成ツールである FabScalar、キャッシュ自動設計ツールである FabCache、およびバスの設計ツールである FabBus から構成されている [1].

#### 2.2 AnyCore

FabScalar の採用している命令セットは古い命令セットであるため、最新の命令セットである RISC-V への対応が求められている。そこで FabScalar をベースとして、RISC-V プロセッサコア自動設計ツールである AnyCore[2] が開発されているが、マルチコアプロセッサとして動作させるために必要な同期命令は未実装である。

### 2.3 RISC-V

RISC-V は非営利団体である RISC-V 基金によって開発・運営されているフリーの命令セットであり、近年開発された最新の命令セットであること、仕様がオープンになっているオープンアーキテクチャであること、および機能ごとに命令をモジュールとして分割し、目的にあった命令のみを実装することができるモジュラー式という方式を採用していることが特徴である.

## 3 提案手法

FabHetero を RISC-V に対応させるには, FabHetero のプロセッサコア生成ツールを現在利用している FabScalar からAnyCore に置き換えることで実現できる.

しかし現在の AnyCore ではマルチコア化するために必要な命令セットである同期命令がサポートされていない. そのため同期命令の実装方法を考案する必要がある. RISC-V において同期命令は RV32A 拡張モジュールにまとめられており, LR/SC命令と AMO 命令の二種類の命令がサポートされる [3].

## 3.1 LR/SC 命令

LR/SC 命令は不可分なメモリアクセスの実現に利用され、LR 命令で値のロード及び監視アドレスの設定、SC 命令で非介入のストアを保証する。FabScalar にも同種の LL/SC 命令があるため、LR/SC 命令の実装は LL/SC 命令の実装を参考にした。

### 3.2 AMO 命令

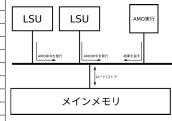

AMO 命令は Atomic-Memory-Operation の略称であり、この命令はメモリの指定したアドレスから値を取得し、その値に二項演算を行い、再び同じアドレスに演算結果を格納する.実行する二項演算としては表 1 がある.RISC-V は命令セットの定義であり、実装方法はハードウェア設計者に委ねられている.そこで、本研究では以下のような実装方法を考案した.AMO命令の実装には図 1 のような専用の AMO 命令実行モジュールを作成した.そして、各コアはそのモジュールに対して AMO 命令要求を行い、命令の実行結果を受け取るというような実装を行った.

| 動作            |

|---------------|

| スワップ (値の入れ替え) |

| 加算            |

| 論理積           |

| 論理和           |

| 排他的論理和        |

| 符号付き最大値       |

| 符号なし最大値       |

| 符号付き最小値       |

| 符号なし最小値       |

|               |

表 1 AMO 命令一覧

図 1 AMO 実行モジュール

### 4 提案手法の評価

今回の手法を実装した LSU を System Verilog で記述しシミュレーションにより動作を確認した。 LR/SC 命令では他のスレッドからの介入がある場合に失敗することを確認し、AMO 命令ではメモリへの値の格納および LSU への結果の返答が成功していることを確認できた。

#### 5 おわりに

本研究では FabHetero へ AnyCore を組み込むための前段階として、AnyCore に対して実装する必要のある命令の実装方式を提案し、評価を行った。今後は本手法の面積評価、及び本手法を用いた AnyCore のマルチコア対応を行う予定である。

### 参考文献

- T. Nakabayashi, et al. FabHetero: An Environment for Developing Diverse Heterogeneous Multi-core Processors., 2nd International Symposium for Sustainability by Engineering at MIU, pp.288-291 (2012)

- [2] R. Chowdhury, et al. AnyCore: A Synthesizable RTL Model for Exploring and Fabricating Adaptive Superscalar Cores., Proceedings of the 2016 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS'16), pp. 214-224 (2016)

- [3] A. Waterman, et al. The RISC-V Instruction Set Manual Volume I: User-Level ISA Document Version 2.2, https://riscv.org/wp-content/uploads/2017/05/riscvspec-v2.2.pdf, (2021-12-13)